本文共 3256 字,大约阅读时间需要 10 分钟。

缓存解决了什么体系结构

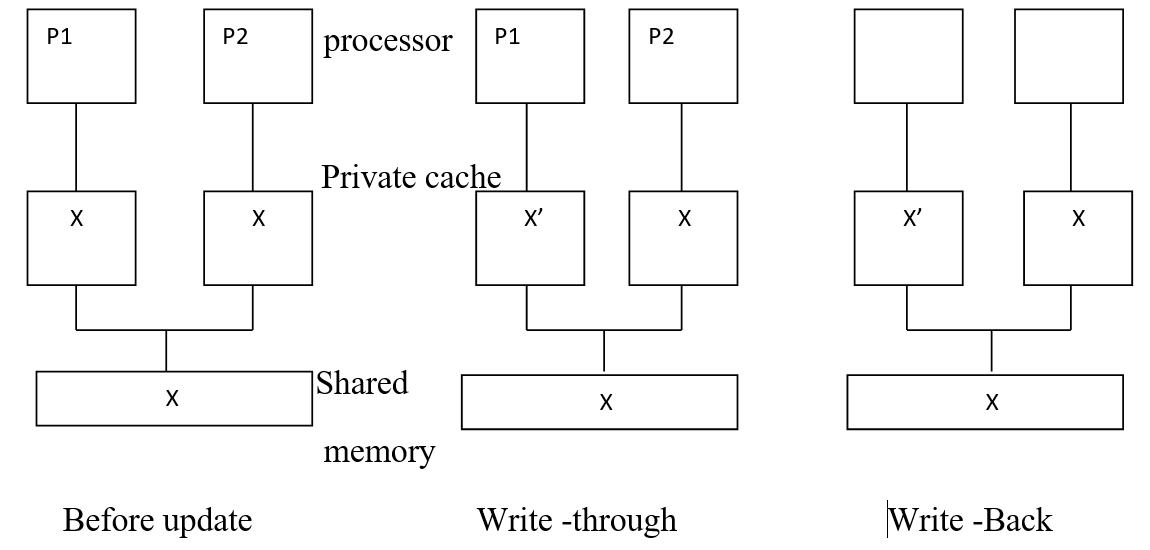

First of all, we will try to understand what cache coherence is? When multiple processors maintain a locally cached copy of a unique shared memory location. Any local modification of the location can result in a globally inconsistent view of memory. Cache inconsistencies are generally caused by data sharing, process migration or input, output. When there occurs an inconsistency in the sharing of co relatable data.

首先,我们将尝试了解什么是缓存一致性 ? 当多个处理器维护唯一共享内存位置的本地缓存副本时。 位置的任何本地修改都可能导致内存的全局不一致。 缓存不一致通常是由数据共享,进程迁移或输入,输出引起的。 当发生相关的数据共享不一致时。

Suppose if a processor A writes some new data X' into the cache the same copy will be written immediately into the shared memory under a write-through policy. In this case, inconsistency occurs between the two copies because if some other write operation can take place before this update.

假设如果处理器A将一些新数据X'写入高速缓存,则根据直写策略,同一副本将立即写入共享内存。 在这种情况下,两个副本之间会发生不一致,因为如果在此更新之前可以进行一些其他写操作。

基于史努比的协议 (Snoopy-Based Protocol)

In this using private cache associated with processor tied to a common bus, two approaches have been practiced for maintaining cache consistency:

在这种使用与绑定到公共总线的处理器相关联的专用缓存的方法中,实践了两种方法来维护缓存一致性:

Write invalidate

写无效

Write Broadcast/ Update policies

编写广播/更新策略

缓存一致性协议 (Cache coherence protocol)

In this section, we will discuss one of the cache coherence protocols that are Directory-Based Protocol.

在本节中,我们将讨论一种基于目录的 协议的缓存一致性协议 。

Cache coherence protocol that does not use broadcast must store the locations of all cached copies of each block of shared data.

不使用广播的缓存一致性协议必须存储每个共享数据块的所有缓存副本的位置。

The list of all cached locations whether centralized or distributed called cached hierarchy.

所有缓存位置的列表,无论是集中式还是分布式的都称为缓存层次结构。

Directory entry for each block of data contains no. of pointers to specify the location copies of the block.

每个数据块的目录条目均不包含。 用来指定块位置副本的指针。

Each directory entry also contains a dirty bit to specify whether a particular cache has permission to write the associative block of data.

每个目录条目还包含一个脏位,以指定特定的缓存是否有权写入关联数据块。

脚步 (Steps)

Cache C3 detects that log containing location is valid but the processor does not have permission to write the block.

高速缓存C3检测到包含位置的日志有效,但是处理器无权写入该块。

Cache C3 issue is written request to the memory module containing location X, the memory modules issue invalidate request to caches C1 and C2.

高速缓存C3的发出是向包含位置X的存储模块的写入请求,存储器模块向高速缓存C1和C2发出无效请求。

C1 and C2 receive the invalidate request set the appropriate bit to indicate that the block containing location X is invalid and sent acknowledged back to the memory.

C1和C2接收将无效请求设置为适当的位,以指示包含位置X的块无效,并将其确认发送回内存。

The memory module receives the acknowledgments sets the dirty bit, clears the pointer to catch C1 and C2 and sends writes permission to cache C3 receives the write permission, update the state in the cache and reactivate processor P3.

存储器模块接收到确认设置脏位,清除指针以捕获C1和C2并向缓存C3发送写许可,接收写许可,更新缓存中的状态并重新激活处理器P3 。

Conclusion:

结论:

In the above article, we have discussed the cache coherence and cache coherence protocol and its steps in brief. I hope till now after reading the above article you have a basic idea of cache coherence. For more queries shoot your questions in the comment section below.

在上面的文章中,我们简要讨论了缓存一致性和缓存一致性协议及其步骤 。 我希望到目前为止,阅读以上文章后,您对缓存一致性有了一个基本的了解。 有关更多查询,请在下面的评论部分中提出您的问题。

翻译自:

缓存解决了什么体系结构

转载地址:http://uwvzd.baihongyu.com/